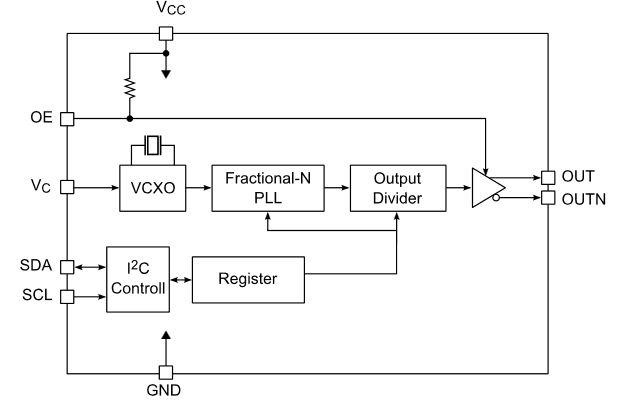

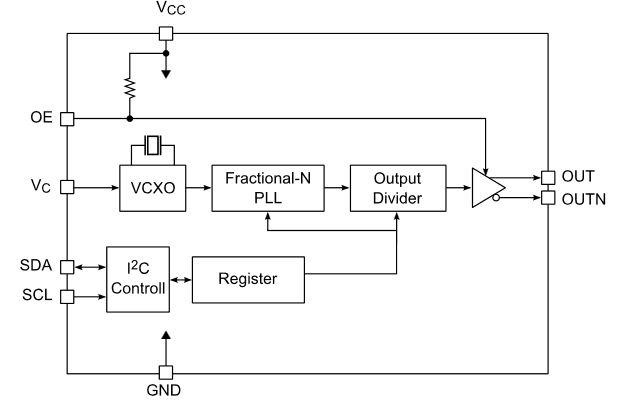

Programmable Voltage Controlled Oscillator: VG7050EAN is a low jitter programmable VCXO at any frequency. VG7050EAN consists of output buffers from VCXO, PLL, and LVPECL. Its output frequency can be programmed from 50 MHz to 800 MHz, with a resolution close to 2 ppb. VCXO provides a stable reference clock for PLL. The Kv of VCXO can be programmed through the 2C interface through I. PLL consists of low jitter step n PLL technology. The components of the loop filter are embedded in the integrated circuit, so no external components are required. The programmable output frequency ranges from 50 MHz to 800 MHz (set decomposition energy: 2.2~2.8 x 10-9), and can achieve a frequency offset of ± 0~± 180 x 10-6 within the frequency control range. The power supply voltage is 2.5 V or 3.3 V, ensuring the normal operation of the equipment. The external size of the product is 7.0 x 5.0 x 1.5 mm, suitable for installation in various devices. Users can specify one startup frequency to ensure that the equipment can start quickly when needed. The equipment adopts low jitter phase-locked loop technology, which can effectively reduce the jitter of the equipment during frequency changes and improve its stability. Suitable for various application fields, including SONET/SDH, OTN, GbE, and Fiber Channel.

·Frequency range: 50 MHz~800 MHz (set decomposition energy: 2.2~2.8 x 10-9)

·Power supply voltage: 2.5 V/3.3 V

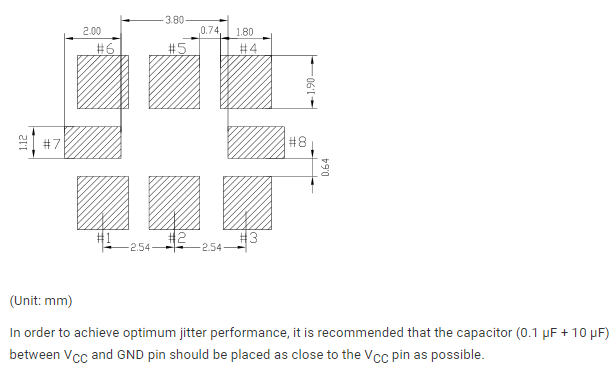

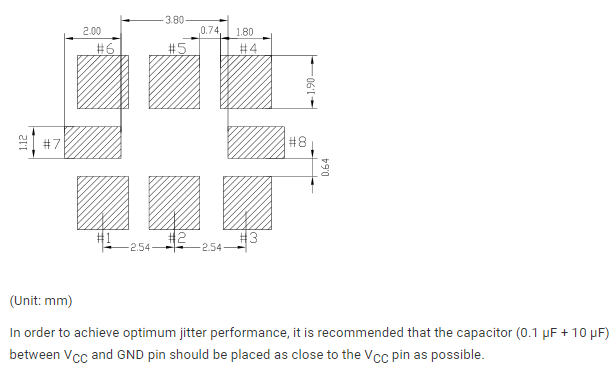

·External size specification: 7.0 x 5.0 x 1.5 mm (8 pins)

·Absolute frequency control range: ± 0~± 180 x 10-6 (12 steps optional)

·Characteristics

·User specified 1 startup frequency

·APR and 7-bit I2C address

·User programming: I2C

·Low jitter phase-locked loop technology

·Application

SONET/SDH, OTN, GbE, Fiber Channel

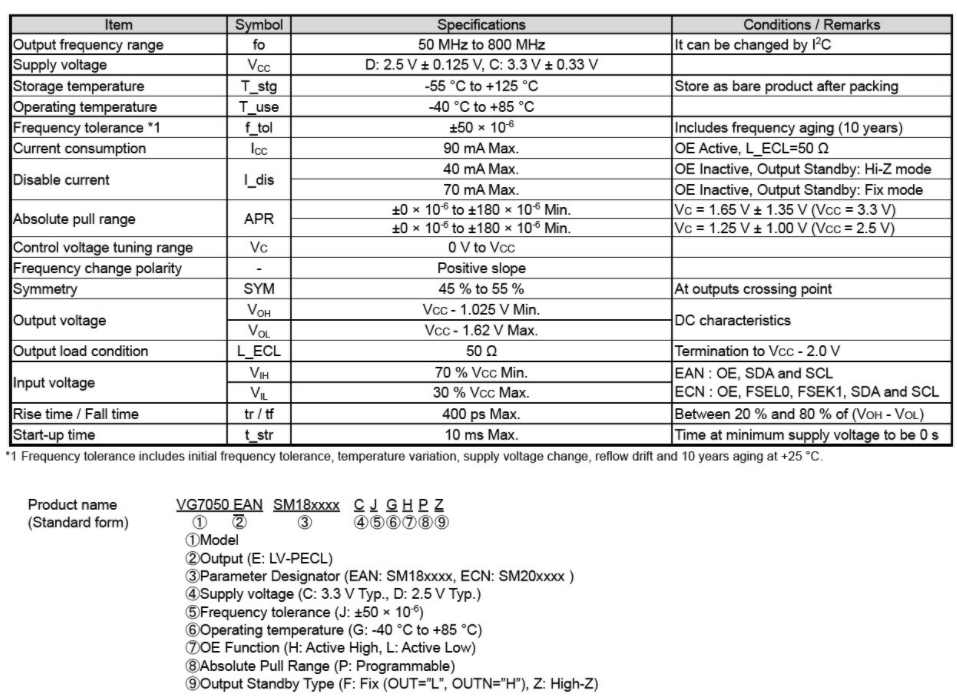

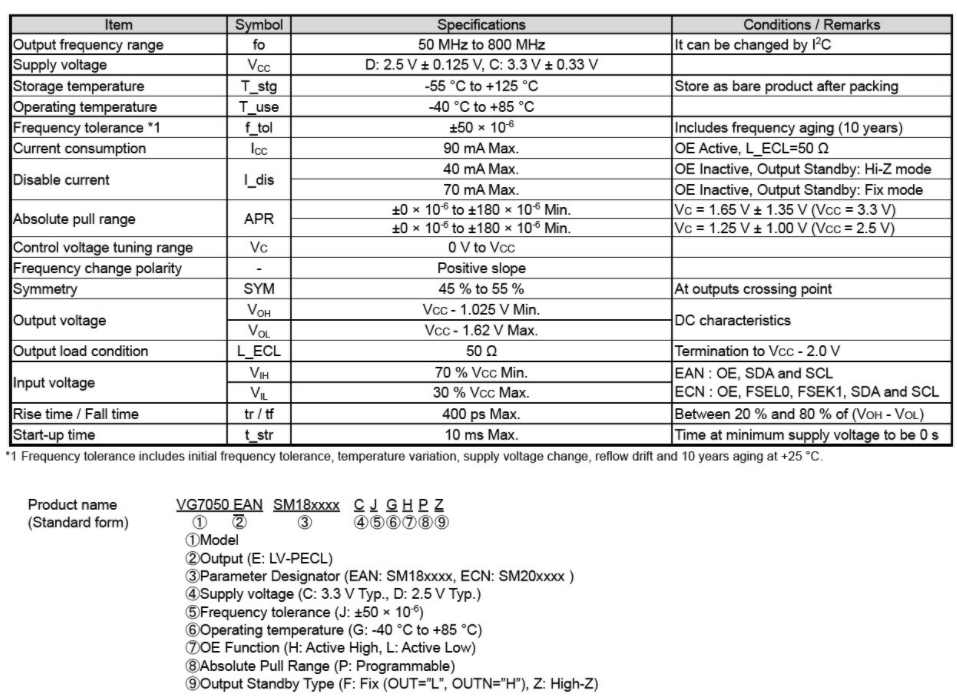

Specifications (characteristics)

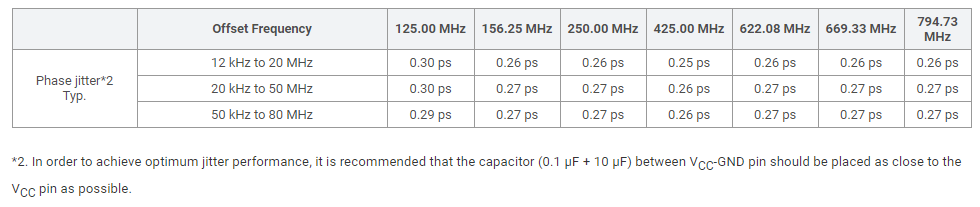

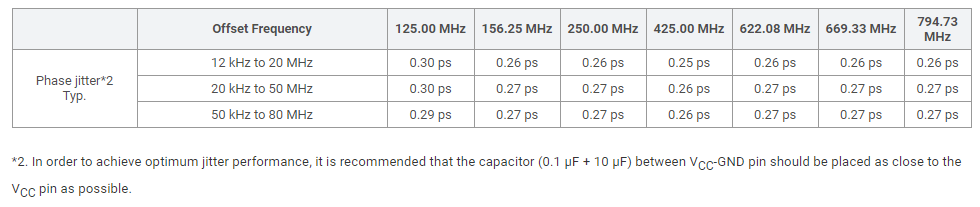

Phase Jitter

Block diagram

Footprint (Recommended)